Model Struktur

Kali ini saya akan melanjutkan pembahasan saya terdahulu tentang Pengenalan Verilog. Pembahasan saya kali ini akan mengarah pada cara untuk membuat suatu modul dengan strukturnya. Salah satu cara termudah untuk membuat suatu model adalah dengan model struktural, dengan mengkoneksikan device secara sederhana. Sehingga akan menjadi satu kesatuan yang disebut dengan rangkaian.

Primitives

Verilog menyediakan dua puluh enam jenis primitives, primitives ini termasuk gerbang logika dan switch, diantaranya xnor, and, nor, berbagai jenis buffer seperti buff, not, pulldown, juga berbagai transistor diantaranya nmos, pmos, dan trans

Ports

Terminal dari suatu koneksi dalam verilog disebut dengan port. Sebagai contoh:

Penulisan gerbang tersebut dalam verilog adalah:

Primitives

Verilog menyediakan dua puluh enam jenis primitives, primitives ini termasuk gerbang logika dan switch, diantaranya xnor, and, nor, berbagai jenis buffer seperti buff, not, pulldown, juga berbagai transistor diantaranya nmos, pmos, dan trans

Ports

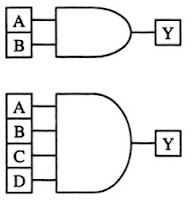

Terminal dari suatu koneksi dalam verilog disebut dengan port. Sebagai contoh:

|

| Gerbang AND |

and (Y, A, B);

and (Y, A, B, C, D);

Ports dalam Modul

Suatu modul dapat memiliki port, apalagi jika dikoneksikan dengan device atau modul lain. Dalam verilog, deklarasi port modul dilakukan dalam dua tempat, yaitu pada bagian dari list modul, juga dideklarasikan dengan arahnya, seperti input, output, atau inout (dua arah).

Hierarki

Hierarki digunakan jika ingin membuat suatu modul yang di dalamnya terdapat modul. Misal untuk membuat mux 2 bit, kita dapat menggunakan dua buah mux satu bit. Dan begitu seterusnya.

Komentar

Posting Komentar