Pengenalan Verilog

Hari ini saya akan memposting tentang cara belajar Verilog yang mudah dan cepat. Selain itu, tujuan saya memposting tulisan ini adalah untk melatih pamahaman dari pembelajaran saya sekaligus sebagai database yang mungkin nanti akan saya perlukan.

Verilog adalah bahasa simulasi yang digunakan untuk perangkat keras, salah satunya adalah FPGA. Bedanya bahasa simulasi dengan bahasa pemrograman adalah, pada simulasi, keterangan waktu ditampilkan, apakah sistem berjalan secara terus menerus atau diskrit.

Untuk tahapan identifikasi atau tahapan untuk menyatakan variabel-variabel yang akan digunakan, verilog memiliki beberapa aturan, yaitu:

1. Boleh mengandung huruf (A-Z, a-z), angka (0-9), garis bawah ( _ ), dan tanda dolar ($)

2. Harus dimulai dengan huruf atau garis bawah

3. Sensitif karakter

4. Panjang karakter bisa mencapai 1024

5. White space (spasi, tab, enter) tidak sensitif dalam Verilog, yang dilarang hanya bila terdapat white space di dalam tanda kurung (" ")

Komentar dalam Verilog ada dua jenis, yaitu comment lines dan block lines. Comment lines diawali dengan tanda // yang merupakan komentar terdiri dari satu baris. Sedangkan block lines diawali dengan tanda */ dan terdiri lebih dari satu baris komentar.

Angka/bilangan yang digunakan dalam Verilog berbasis desimal, apabila kita ingin menyatakan suatu bilangan dengan menggunakan basis lain seperti biner atau heksadeimal, maka penulisan bilangan tersebut adalah sebagai berikut: jumlah bit'radix(spasi)nilai bilangan. Contoh: 8'b10100101

Dari contoh tersebut angka 8 menunjukkan jumlah bit yang digunakan, default yang digunakan dalam Verilog adalah 32 bit. Huruf 'b menunjukkan basis biner,sementara untuk basis heksadesimal digunakan 'h atau 'H dan basis oktal digunakan 'o atau 'O.

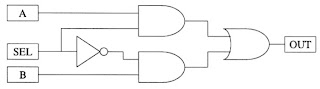

module mux (OUT, A, SEL, B);

output OUT;

input A, SEL, B;

not I5 (sel_n, SEL);

and I6 (sel_a, A, SEL);

and I7 (sel_b, B, sel_n);

or I4 (OUT, sel_a, sel_b);

end module

Pada awal modul, kita deklarasikan nama modul (module mux) dan port apa saja yang digunakan (OUT, A, SEL, B). Kemudian, deklarasikan output apa yang akan digunakan (OUT), dan input yang digunakan (A, SEL, B). not, and, dan or menyatakan gerbang apa saja yang digunakan, sementara I4, I5, I6, dan I7 hanya menyatakan permisalan nama untuk masing-masing gerbang tersebut. Kolom pertama pada tiap tanda kurung menyatakan output, sementara yang lainnya adalah inputnya. Untuk mengakhiri program digunakan end module.

Saat ini, sampai di sini dulu pengenalan saya tentang Verilog. Pada postingan berikutnya, saya akan membahas tentang model struktural dari pemrograman menggunakan verilog. Namun sebelumnya, saya akan melampirkan sebuah buku teks yang menjadi referensi saya dalam belajar. Untuk mengunduh, klik di sini: Veriliog Quickstart Guide

Semoga bermanfaat

Wah,sama2. Senang bisa membantu

BalasHapus