Objek Data dalam Verilog

Pada posting kali ini, saya akan membahas beberapa tipe data yang dapat dikerjakan dengan verilog, yaitu: nets, regs, integers, times, parameters, events, dan string.

- Nets, disebut juga dengan wire, merupakan salah satu bentuk objek data yang paling umum digunakan dalam verilog. Nets digunakan untuk menghubungkan antara module dengan primitives yang telah kita bahas sebelumnya pada postingan Model Struktur. Berbagai tipe nets merepresentasikan wired OR, wired AND, titik terminal, pull up, dan pull down. Tipe default dari nets adalah wire murni tanpa karakteristik khusus. Berikut ini adalah tipe-tipe nets: wire, merupakan tipe default dari nets; tri, nama lain dari wire; wand, wired and; triand, nama lain dari wand; wor, wired or; trior, nama lain dari wor; tri1, wire dengan pull up; tri0, wire dengan pull down; supply1, selalu bernilai 1; supply0, selalu bernilai 0; trireg, titik terminal dengan mode switch. Wire dan tri merupakan tipe net yang sama, perbedaannya hanya terletak pada perbedaan tiga kondisi dengan yang tidak, yaitu high, low, dan impedansi tinggi. Dalam verilog, wire pada umumnya menampung data sebesar 1 bit, untuk data yang lebih besar dari satu bit, wire disebut dengan vector. Untuk mendeklarasikan data lebih dari 1 bit, digunakan deklarasi range. Range digunakan untuk menentukan jumlah bit, sebagai contoh, range [7:0] menunjukkan 8 bit data. Contoh deklarasi net:

wire [7:0] d, e, f; //merupakan 8 bit vektor

trior [26:2] data_bus; //merupakan 25 bit vektor

- Ports, deklarasi port seperti pada pembahasan di posting Model Struktur, secara otomatis akan menyebabkan munculnya net dengan tipe default dengan range yang sama sebagai ports.Contoh module untuk deklarasi port:

input [7:0] a; //menyebabkan wire [7:0] a

inout [7:0] c;

triand [7:0] c; //driver multiple pada c akan di and kan

- Regs, digunakan untuk memodelkan block prosedural. Contoh deklarasi register:

reg [8:15] d, e, f, g; // Empat register 8-bit

Ingat bahwa bit paling kiri merupakan most significant bit, atau angka yang paling besar.

Untuk menyeleksi range, dapat digunakan contoh deklarasi sebagai berikut:

e[15] // Mengacu pada least significant bit dari e

d[8:ll] // Mengacu pada empat most significant bit dari d

Memory, merupakan array dari register. Cara pendeklarasian memory sama dengan register.Verilog

menggunakan 2 bit dari memori komputer untuk mensimulasikan tiap bit memory, karena tiap bit

simulasi memory dapat bernilai 0, 1, x, atau z. Contoh pendeklarasian memory adalah sebagai berikut:

reg [7:0] a, b[0:15], c[971:960];

reg d, e[8:13];

a [3]; // mengacu pada bit tiga dari register a

b [3]; // mengacu pada words 8-bit keempat pada memory b

Pada baris pertama, a adalah sebuah register 8-bit, b adalah sebuah memory yang berisikan enam belas

words 8-bit, dan c adalah dua belas words 8-bit. Sedangkan pada bnaris kedua, d merupakan sebuah

register 1-bit, dan e adalah enam words 1-bit.

Initial value, atau nilai awal dari suatu register adalah 'bx (unknown). Jadi jika ingin nilai awal telah

ditentukan, maka dapat diinisialisasikan terlebih dahulu. Contohnya:

reg [7:0] a; // nilai awal adalah 8'bx;

reg [7:0] b = 8'd3; // nilai awal adalah 3

reg [3:0] c, d=3, e=4;

- Integers dan Real, memiliki lebar 32-bit. Perbedaan diantara keduanya adalah real memiliki floating point. Integer dideklarasikan dengan kata integer sedangkan real dideklarasikan dengan kata real.

- Time dan Realtime, merupakan double integer (biasanya terdiri dari 64 bit)

- Parameter, merupakan konstanta dari waktu yang berjalan. Tipe default dari parameter adalah integer (32-bit), namun parameter juga dapat berupa string. Contoh deklarasi parameter: parameter message = "Hello Verilog"; parameter size =8; parameter delay =3; parameter prog = size*delay parameter msb = size-1; parameter low = 0; wire [msb:0] a; // parameter msb +1 adalah lebar a; reg [size-1:low] b; // lebar ukuran dan low

- Event, digunakan untuk sinyal yang mentrigger terjadinya perubahan.

- String, disimpan dalam long register 8-bit (1 byte) utnuk menyimpan tiap karakternya.

- Multidimensional Array. Contoh : reg [7:0] bus, rom[0:255], screen[0:1023][0:767]; rom [5] // sebuah 8 bit word dari rom rom [5] [6] // Sebuah bit dari sebuah words pada sebuah rom screen [1][2] // sebuah 8 bit word dari screen screen [1] [2] [3] // sebuah bit dari screen screen [1] // tidak diperbolehkan

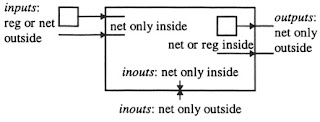

Perlu diperhatikan bahwa output boleh dideklarasikan sebagai register, namun input dan inout hanya boleh dideklarasikan sebagai nets. Untuk mrndeklarasikan output sebagai register, pertama-tama deklarasikan sebagai output, kemudian deklarasikan lagi sebagai register. Berikut ini adalah contoh hubungan antara port dan register:

|

| hubungan antara port dan register |

Komentar

Posting Komentar